## Tech Brief

# Power Electronic Fabrication Choices Vital to Performance and Yield

DIRECT BONDED COPPER • ACTIVE METAL BRAZING • THICK PRINT COPPER

## INTRODUCTION

Many solid-state power electronics, including those used in high-powered LED, RF/Microwave, electric vehicle, train and rail, electrical infrastructures, and military applications rely on physically and thermally robust ceramic materials as a base. These ceramic materials are bonded to thermally and electrically conductive metals to help transfer thermal energy to heat spreaders/ heat sinks and away from the critical device or component active areas, while electrically insulating the power electronics from grounded shielding and enclosures.

Due to the diversity of solid-state power electronic devices and components, as well as the applications, there is a wide range of substrate fabrication technologies and pre-processing that can be done. Choosing among the various options and prefab processing stages necessary to prepare a ceramic material, or substrate, for fabrication can be a challenge in and of itself.

This technical brief includes a discussion of several of the most common power electronic substrate fabrication methods and associated prefabrication processing steps essential to meeting high-power electronic performance requirements for a wide range of applications. Further insights regarding the impact that ceramic material choices have with each substrate fabrication process are also detailed.

#### Power Electronic Substrates

Typical power electronic substrates are comprised of a ceramic base material bonded to a metal layer. This enables the creation of a mechanical and environmentally robust substrate from which power electronic devices can be placed and temperature cycled reliably, while the substrate disperses the waste heat to the assembly body or a heat sink. Furthermore, the adhesion between the ceramic material and metal layer help to prevent the metal—which typically has a much higher coefficient of thermal expansion than the semiconductor and ceramic—from expanding at higher temperatures and damaging the semiconductors used in the power electronic components and devices. In this respect, ceramic material-based substrates can outperform organic-insulator substrates, as a ceramic material better maintains its dimensional stability over time while the organic-insulative substrates deteriorate over time.

Having a thicker insulating substrate (thicker ceramic base material) negatively impacts the thermal conductivity of a substrate, but also simultaneously increases the electrical insulation of the substrate, which must be consid-

Electric Car Lithium Battery Pack

The high voltage and current carried by electric vehicle chargers, inverters, and switches rely on high power solid state electronics built on robust ceramic substrates. ered prior to selecting a ceramic material and substrate thickness. Moreover, having a closer CTE to the semiconductor of the power device is desirable for larger die sizes, as less mechanical strain will be induced on the chip during temperature cycling.

There are several common methods and combinations of ceramic material and metal to develop a power electronic substrate. These include Direct Bonded Copper (DBC), Active Metal Brazing (AMB), and Thick Print Copper (TPC). This section will describe the features of these substrate fabrication methods and how they pair with the various ceramic substrates.

#### **Direct Bonded Copper (DBC)**

DBC is a very common process in which a copper oxide (eutectic bond) is formed between a copper sheet to the oxides in the ceramic substrate in a nitrogen and oxygen atmosphere and at very high temperatures—near 1070 degrees Celsius. With DBC no interlayer material is necessary, but the temperature must be kept below 1085 degrees Celsius, as copper melts at this temperature. DBC is often a two-layer process, where the back of the substrate is a solid and unfeatured sheet of copper, and where the top copper layer is structured using chemical etching, or is performed to develop the electrical circuit traces. The bottom copper layer is most often soldered to a heat spreader or heatsink.

Due to the relatively low cost of the process, alumina is often used with the DBC process to develop low-cost substrates. However, the sensitivity of the eutectic bonding with DBC makes developing a high-yield mass production process of large DBC cards challenging.

AIN and BeO are also used to make DBC substrates. Though more expensive, AIN and BeO bases offer much greater thermal conductivity than alumina, with AIN being seven to eight times more thermally conductive and BeO being twice again as thermally conductive as AIN. AIN also offers a much closer CTE to Si and SiC semiconductor chips than alumina, but is also mechanically weaker than either alumina or BeO. Hence, for the same mechanical strength, a much thicker slab of AIN is needed. AIN DBC substrates also require an additional precision lapping and controlled oxidation stage to achieve proper eutectic bonding.

The thick copper-foil and high-performance ceramic materials enable DBC substrates to be very mechanically robust and reliable with good thermal conductivity. The thick copper of a DBC substrate also exhibits excellent electrical conductivity, while the thick ceramic provides substantial electrical insulation between the top circuit layer and grounded bottom layer. Solder and thick-wire stages are also readily performed on DBC substrates.

#### Comparison of Direct Bonded Copper and Thick Film Copper High Power Substrate Fabrication Processes

DBC process technology steps

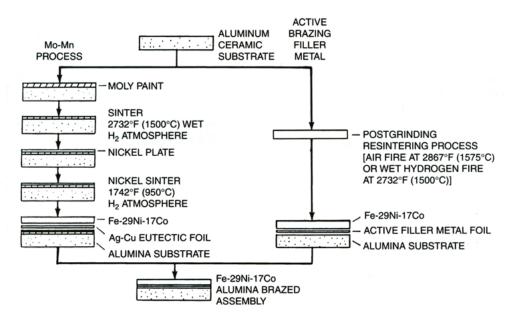

#### Active Metal Brazing (AMB)

With AMB a metal foil, typically copper, is bonded to a ceramic using a vacuum brazing process. Silver and copper, with additional titanium or indium brazing materials are most often used during AMB. AMB temperatures range from 800 to 1000 degrees Celsius, which is generally 50 to 100 degrees Celsius above the braze alloys melting temperature. AMB substrates are made in a vacuum or inert atmosphere to prevent chemical action of the highly reactive braze alloys.

AMB substrates are most often composed of alumina or AIN. Alumina AMB substrates can benefit from a thicker copper-foil layer than AIN AMB substrates, as the greater mechanical strength of alumina helps prevent damage to the semiconductor from the metal-to-semiconductor CTE mismatch. Thicker copper in an AMB substrate enables greater current-carrying capacity and improved heat spreading compared to thinner copper AMB substrates, which could translate to better thermal control of a power device or a subsequently smaller power device die size.

Another process that uses brazing is Direct Bonded Aluminum (DBA), which actually uses an aluminum-silicon (AlSi) composite to bond thick aluminum foil to a ceramic. Though aluminum exhibits less thermal and electrical conductivity than copper, the softer aluminum foil also imparts less physical strain on the semiconductor chip during temperature cycling. Hence, DBA substrates can typically undergo many more thermal cycles than DBC or AMB with copper foil.

Active Metal Brazing Process Steps

#### Thick Print Copper (TPC)

A TPC substrate is fabricated by applying a copper-powder paste via screen printing to a ceramic substrate and then firing the piece between 850 and 950 degrees Celsius to sinter the copper powder to the ceramic. TPC creates a high-adhesion bond between the metal and ceramic, which enables extreme reliability during temperature cycling. Moreover, with TPC, thick and wide copper traces, as well as thin and narrow copper traces, can be developed on the same substrate, allowing for logic, analog, RF, and high-power circuits to be developed simultaneously.

Very thick silver and copper conductors, between 25 and 300 micrometers, can be developed on a wide range of ceramic substrates. Unlike other substrate fabrication processes, TPC substrates can be built with through-hole interconnects, which can be used to develop multi-sided circuits or high thermal conductivity vias for enhanced thermal dissipation. TPC substrates have been used for the past several decades in military, automotive, aero-space, and other high-power applications that require extreme reliability.

The ceramic and metal bond can also be tailored with the TPC process to control the bond depth in the ceramic. Furthermore, the metal paste can be enhanced with adhesion promoting materials, such as glass and oxide materials, to tailor the CTE of the TPC substrate to better match the semiconductor of the power-device die. TPC substrates can also be fabricated with standard assembly processes, such as soldering and thick-wire bonding.

Newer technologies, similar to TPC, are silver sintering and silver soldering. These methods use silver (Ag) metal powder or tin-silver (SnAg) to develop very thermal- and electric-conductive traces on a ceramic base material. Both the silver soldering and sintering processes require extremely precise temperature and timing control. The ceramic base material's surface finish must also be well-matched to the process to enable proper adhesion.

| Properties                         | DBC                                | Thick Film Copper                   |

|------------------------------------|------------------------------------|-------------------------------------|

| Typical Cu Thickness               | 300 µm                             | 300 µm                              |

| Min. Cu Thickness (µm)             | 80 µm                              | 20 µm                               |

| Min. Line/Space (µm)               | 600 at 300 µm thickness            | 250 at 300 µm thickness             |

| Electrical Resitivity              | 1.65x10-8 (Ωm)                     | 2.62x10-8 (Ωm)                      |

| Thermal Conductivity (full system) | 242 (W/mK)                         | 174 (W/mK) (290 W/mK for AIN)       |

| Warpage Variation                  | Strong                             | Very Low                            |

| Design freedom (line resolution)   | Limited                            | Excellent                           |

| Reliability                        | Dimples for acceptable reliability | Excellent                           |

| Process Difficulty                 | Easy                               | Easy                                |

| Cost                               | Low                                | Medium, depends on number of layers |

#### Prefab Processing of Ceramic and Semiconductor Substrates

The surface finishes, thicknesses, camber, and parallelism of the ceramic materials are critical to the success of every substrate fabrication process. Moreover, consistency between batches of a ceramic material could greatly affect the overall reliability and performance of a power electronic device or assembly product line. Hence, control of the lapping and polishing processes is essential when designing and manufacturing electronics for high-power applications, which require high reliability and consistent performance.

Though it is common to believe that lapping and polishing a ceramic can either be done to the minimum required specification to reduce cost, or to make the ceramic material as smooth as possible, neither of these solutions will likely produce a viable ceramic material for a power electronics application. The exact surface finish, thickness, and parallelism must all be determined and tailored to a specific substrate fabrication process, and be accurately replicated from batch to batch. Moreover, surface thickness must be specified to coincide with the precision of the circuit traces on the metal layer. Higher precision of the metal traces typically requires a surface finish to be specific to the process.

The surface finish is a critical aspect in adhesion of the metal layers with the ceramic material, and too rough or too fine a surface finish could result in unreliable adhesion, resulting in delamination, overheating, or early device failure. Lapping and polishing are two prefabrication processes that are used to precisely control the surface finish. However, each ceramic material can only be lapped or polished to its individual surface finish limit. Lapping and polishing are trace finishing also requires greater processing time, which must be accounted for in the supply chain process.

The thickness of ceramic materials is also a determining factor in the tradeoff of a substrate's thermal conductivity and electrical insulation characteristics and must be precisely controlled. Lapping is typically used to remove material from one or both sides of a ceramic base plate to produce a very controlled thickness dimension. The more exacting the dimensions and tolerances, a more precise and time-consuming lapping process is required,

#### **Precision Lapping**

Lapping helps to ensure a substrate meets the piece-to-piece and batch-to-batch consistency and dimensional tolerances necessary for developing a high yield high power electronics fabrication process. as finer abrasives will need to be used to ensure greater precision. For even more thickness precision, a polishing stage can be performed, which can remove material thickness and enhance surface finish.

Both flatness and parallelism of a ceramic base material are also important for a high-yield power electronics fabrication process. Poor flatness and parallelism of a ceramic material can lead to inconsistencies with a substrate metal layer adhesion, thermal conductivity, and electrical insulation. For TPC, and other printed applications, poor flatness and parallelism may also lead to inaccuracies with trace thickness and placing during printing.

Generally, a lapping process is used to enhance the ceramic's as-fired camber and parallelism to a very high degree. The majority of lapping machines are single-sided lappers, but there are also double-sided lapping machines that deliver process speed and performance improvements over single-sided lappers.

A double-sided lapping machine manned by a skilled technician can achieve the most accurate parallelism and flatness, and typically requires less processing time to achieve a desired thickness, compared to single-sided lapping options. For optimum consistency, in cases where processing tolerances must be near-identical from piece to piece and batch to batch, a double-sided lapper can rapidly deliver a thickness tolerance of +/- 0.0001 inches over 4.5 inches.

A polishing stage can be used after lapping to improve surface finish and thickness tolerance in cases where extreme control of these parameters is required. With improved flatness tolerance, a double-sided lapping process also enables improved polishing performance over single-sided lapping.

**Precision Polishing** Polishing can further enhance the dimensional tolerances of lapped substrates, and greatly improve the surface finish when necessary.

## CONCLUSION

Ultimately, the reliability, performance, and yield of the manufacturing of a power electronic substrate depends on the precision and quality of a ceramic base materials lapping and polishing process. Hence, the right choice in an industrial ceramic finish supplier can be the difference between power electronics that last for minutes in the field and a tarnished reputation from early device failures, and contract renewals and referrals. Moreover, dependable sourcing of ceramic materials is also essential for having a consistent supply chain for developing ceramic-based power electronic substrates. Having these two features in a single finished ceramics supplier can be a major benefit when establishing new product lines or bolstering an existing produce line with a second supplier source.

#### Next Steps:

Learn more by downloading these pieces of related content: <u>5 Keys to Successful Process-</u> <u>ing of Ceramic Substrates Brief</u> and <u>Selecting</u> <u>the Right Substrate for High Power Brief</u>.

You can access our entire library of technical briefs and design guidelines by visiting our <u>support page</u>.